チップ部品を簡単・正確に測定する方法

近年の基板実装技術は、スマートフォンなどの情報端末や家電製品が小型化・軽量化・薄型化され、チップ抵抗器やセラミックコンデンサなど電子部品のサイズの小型化、そして、電子部品の小型化により基板の実装の高密度化と、実装技術の難易度が増加しています。ここでは、電子デバイスや基板実装技術における問題とその評価、解析に用いられた白色干渉計搭載 レーザ顕微鏡、ワンショット3D測定器の活用事例を紹介します。

- チップ部品の実装方法

- リフローとは

- リフロー炉の温度制御(鉛フリー)

- 表面実装で発生するトラブル

- 基板の反り測定事例

- アルミ電解コンデンサ端子のコプラナリティ測定事例

- クリームはんだの厚み測定事例

- 抵抗膜の厚み測定事例

- 抵抗皮膜のクラック・トリミングの深さ測定事例

- グリーンシートのパターン幅測定

チップ部品の実装方法

電子部品の小型化と基板実装の高密度化に伴い、はんだ付け方式はリフローが主流になっています。

| はんだ付け方式 | 特徴 | |

|---|---|---|

| 長所 | 短所 | |

| はんだごて |

熱によるストレスが小さい |

温度のバラつきが大きい |

| ホットエアー |

熱によるストレスが小さい |

温度のバラつきが大きい |

| レーザ |

|

量産に不向き(処理時間が長い) |

| パルスヒート |

|

量産に不向き(処理時間が長い) |

| リフロー(赤外線式) |

|

|

| リフロー(温風式) |

|

|

| フローはんだ |

|

|

リフローとは

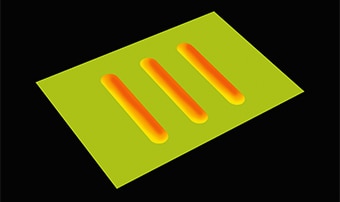

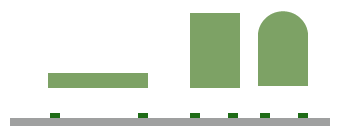

フラックスと顆粒状の小さなはんだ(数十ミクロン)が均一に混合されたクリームはんだ(はんだペースト)を、穴の空いた金属板(メタルマスク)の上に供給し、スキージ(へら)で薄く伸ばして印刷した後、部品を載せて加熱、はんだ付けする方法のことです。

部品点数が少ない場合は、手作業で実装できます。

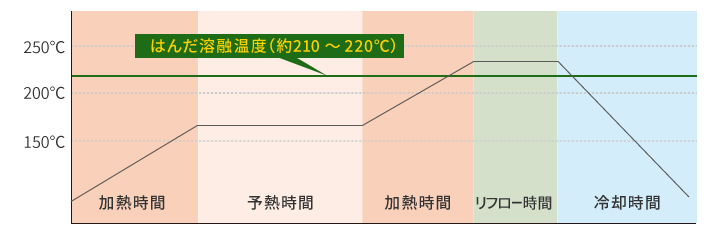

温度は5段階で制御します(下記参照)。

リフロー炉の温度制御(鉛フリー)

通常は、2段階で加熱します。最初の加熱で基板の温度を均一に保ち、2回目の加熱でクリームはんだを溶融します。加熱温度および時間は、リフロー炉の種類や、使用される部品に応じて変化します。

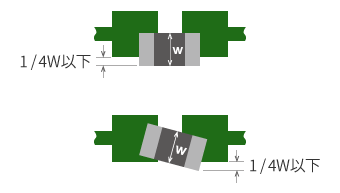

表面実装で発生するトラブル

基板の反り測定事例

通電時の温度上昇や周囲環境の温度変化による基板の反りで、経年変化による実装不良が発生しないかを解析します。常温から260℃の高温までの温度変化で生じる基板の反りを測定できます。

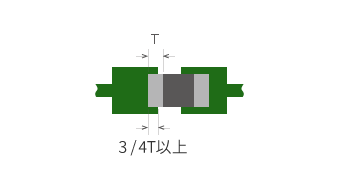

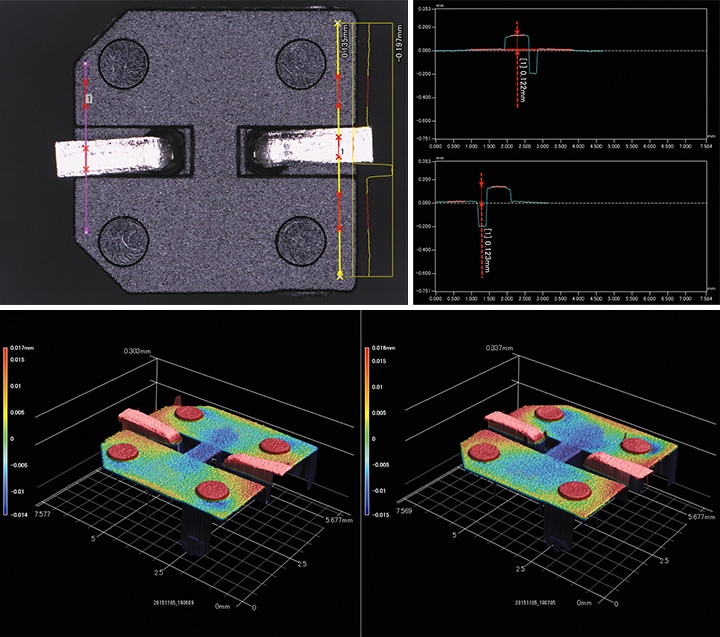

アルミ電解コンデンサ端子のコプラナリティ測定事例

基板実装の不良や実装強度に影響があるコンデンサ端子の平坦度を測定できます。

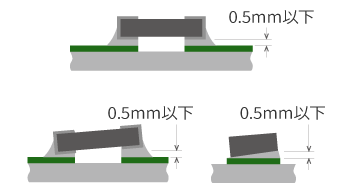

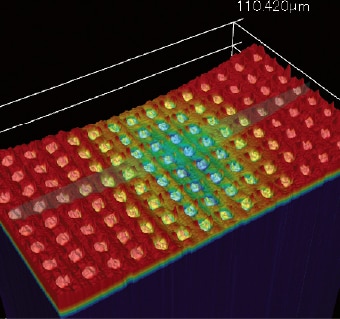

クリームはんだの厚み測定事例

基板に塗布されたクリームはんだの膜厚を測定できます。

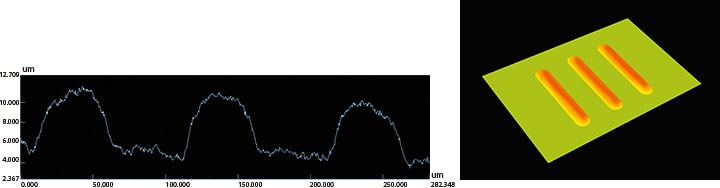

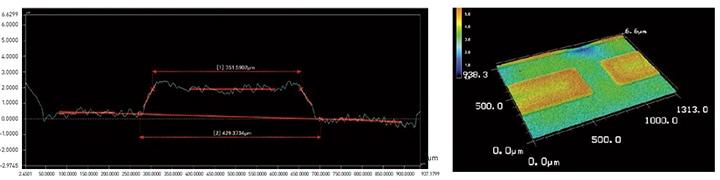

抵抗膜の厚み測定事例

シルク印刷で転写された焼結前のウェットな状態の抵抗膜の厚み、体積が測定できます。

ウェットな状態での膜厚が測定できるので、季節や天候、焼結工程の条件出しが効率よくできます。

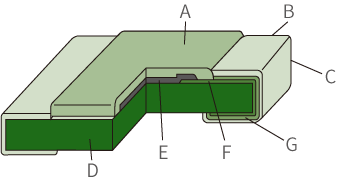

チップ抵抗器の構造

チップ抵抗器とは、磁器などの絶縁基体の表面に抵抗素子を形成し、両端に電極を設け、主として表面実装に適する角板形の小形固定抵抗器のことです。

角形チップ抵抗器の一般的な構造

- (1)端子電極にリード線が無い

- (2)はんだ付け、またはボンディングができる

※メルフ型(円筒形)もありますが、あまり使用されません。

- A

- 保護膜

- B

- 外装めっき

- C

- 端子電極

- D

- セラミック

- E

- 抵抗皮膜

- F

- 内部電極

- G

- ニッケルめっき

- セラミック(基板)

- 抵抗体の焼結、トリミングに耐えられるようにセラミックの板でできています。

- 抵抗体

- 厚膜、薄膜の種類があります。

- 電極

- 抵抗体を内部電極を介して端子電極へ接続します。3層程度の構造になっています。

- 保護膜

- 抵抗体表面に直接湿気や塵埃が付着しないように樹脂やガラスを塗布します。

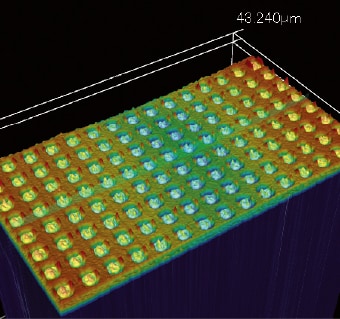

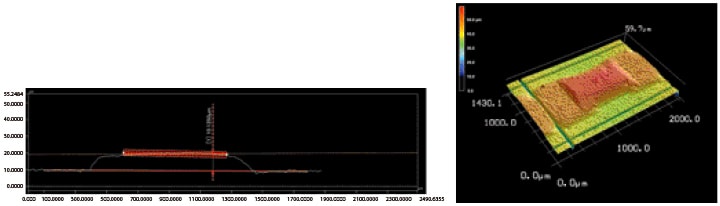

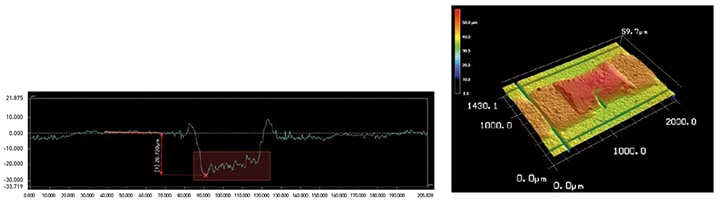

抵抗皮膜のクラック・トリミングの深さ測定事例

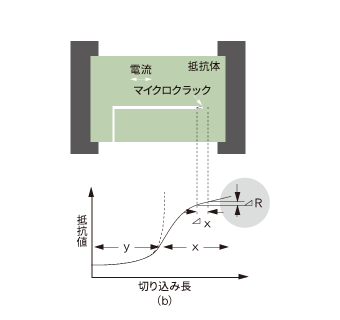

チップ抵抗の値が規格内に入るように管理するため、抵抗膜のトリミングの長さ、深さが測定できます。

また、トリミング部に生じるクラックの幅、深さ測定もできます。

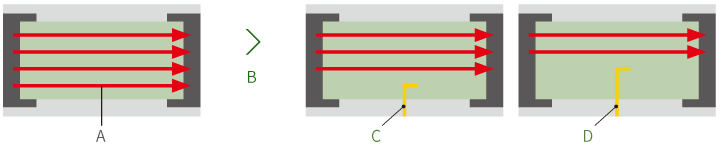

レーザトリミング

チップ抵抗器はスクリーン印刷で各層を形成しています。セラミック基板上に数百以上の抵抗体形成をおこないますので、わずかな印刷状態のバラつきが抵抗値のバラつきに直結します。

抵抗値にバラつきがあるままでは、チップ抵抗器として電気的特性が定格内に入りませんので、抵抗値を調整する工程「レーザトリミング」が必要になります。レーザトリミングは抵抗体を一素子ずつ測定しながら、レーザでカットしていき、狙いの抵抗値にするとともに、バラつきを小さくする工程です。

- (1)あらかじめ目標抵抗値より低め狙いで抵抗体を印刷

- (2)抵抗体にトリミングを入れることで電流経路が狭くなり、抵抗値が上がる

- (3)狙いの抵抗値でトリミングを止め、チップ間のバラつきを小さくする

- A

- 電流の流れ

- B

- レーザトリミング

- C

- トリミング量が小さいと抵抗値変化「小」

- D

- トリミング量が大きいと抵抗値変化「大」

※トリミングで切り上げられた分、抵抗体の電流経路が狭くなるので抵抗値が上がる

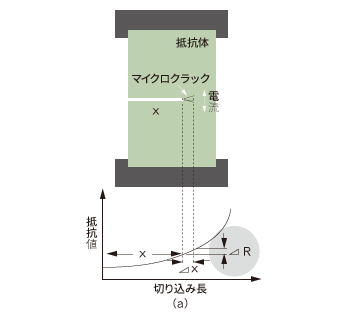

トリミング中の抵抗値変化から最終トリミング長やトリミング形状を決定

形状が直線カットとLカットの場合のカット長による抵抗値変化を示すと、Lカットは最終カット部での精度が高く、かつ終端でのマイクロクラックの影響を小さくできます。

グリーンシートのパターン幅測定

ウェットな状態のグリーンシート(誘電体)のパターン幅、厚みが測定できます。

チップ積層セラミック・コンデンサの構造

誘電体を挟んだ2枚の電極板がコンデンサの基本構造になります。

- (1)セラミック誘電体材料となる、チタン酸バリウム BaTiO3など誘電材料をキャリアフィルムの上に塗布

- (2)これを乾燥させ、グリーンシートを作成

- (3)グリーンシートの上にパラジウム、銀、ニッケルなどを含んだペースト状電極材料を印刷

- (4)10 〜 1000層を重ねて圧着、切断

- (5)焼成し、外部端子を銀めっきすることで、チップ積層セラミックコンデンサが完成

セラミックの焼成では10%ほど収縮するため、これを見越した寸法設計が重要になります。

- A

- 外部電極

- B

- 内部電極

- C

- セラミック誘電体

コンデンサの静電容量は、電極板の面積に比例

複数のコンデンサを並列接合すれば、電極面積が増えることと同じなので、コンデンサの数に応じて静電容量をアップできます。

しかし、これでは回路基板で占める容積が大きくなり、省スペース化できません。

そこで、積層セラミックチップコンデンサは、セラミック誘電体と内部電極をサンドイッチ状に交互に多層積層し、小型化と大容量化を実現しています。